- 您现在的位置:买卖IC网 > Sheet目录338 > LTC3207EUF-1#TRPBF (Linear Technology)IC LED DRIVR QVGA DISPLAY 24-QFN

LTC3207/LTC3207-1

OPERATION

The LTC3207/LTC3207-1 are receive-only (slave) devices.

Sub-Address Byte

There are two

I 2 C

addresses available. The LTC3207

I 2 C

MSB

LSB

address is 00110110 and the LTC3207-1 I 2 C address is

00110100. The I 2 C address is the only difference between

the LTC3207 and the LTC3207-1.

7

X

X

6

X

X

5

X

X

4

X

X

3

0

0

2

0

0

1

0

0

0

0

1

Register

REG0

REG1

Function

COMMAND

ULED1

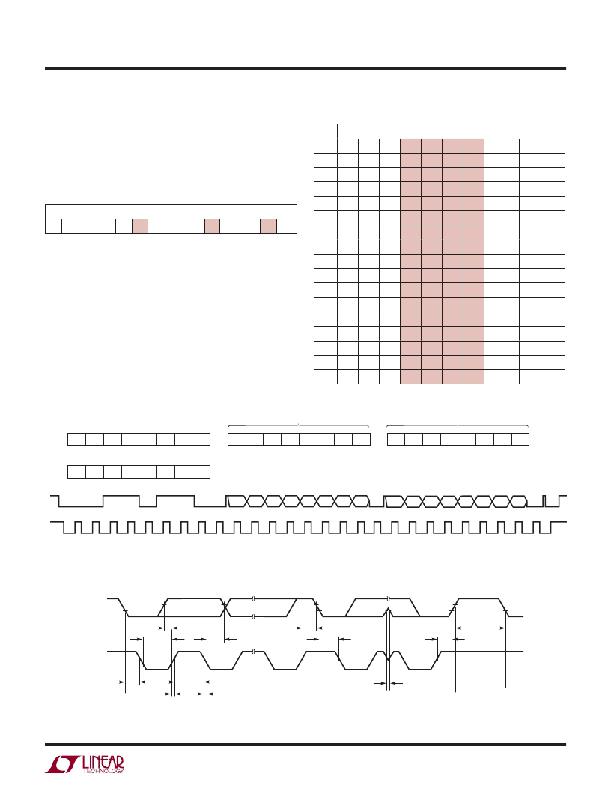

Write Word Protocol Used by the LTC3207/LTC3207-1

1 7 1 1 8 1 8

S Slave Address Wr A *Sub-Address A Data Byte

S = Start Condition, Wr = Write Bit = 0, A = Acknowledge,

P = Stop Condition

1

A

1

P**

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

0

0

0

0

0

0

0

1

1

1

1

1

0

0

1

0

1

0

1

0

REG2

REG3

REG4

REG5

REG6

ULED2

ULED3

ULED4

ULED5

ULED6

*The sub-address uses only the ?rst four bits, D0, D1, D2 and D3

**Stop can be delayed until all of the data registers have been written

Bus Speed

The I 2 C port is designed to be operated at speeds of up

to 400kHz. It has built-in timing delays to ensure correct

operation when addressed from an I 2 C compliant master

device. It also contains input ?lters designed to suppress

glitches should the bus become corrupt.

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

0

1

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

1

0

0

1

1

0

0

1

1

1

0

1

0

1

0

1

0

1

REG7

REG8

REG9

REG10

REG11

REG12

REG13

REG14

REG15

ULED7

ULED8

ULED9

ULED10

ULED11

ULED12

CAM

ENU

G/B/ENU

SUB-ADDRESS

DATA BYTE

LTC3207

ADDRESS

WR

0

0

1

1

0

1

1

0

S7

S6

S5

S4

S3

S2

S1

S0

7

6

5

4

3

2

1

0

LTC3207-1

ADDRESS

WR

0

0

1

1

0

1

0

0

START

STOP

SDA

0

0

1

1

0

1

1

0

ACK

S7

S6

S5

S4

S3

S2

S1

S0 ACK

7

6

5

4

3

2

1

0

ACK

SCL

1

2

3

4

5

6

7

8

9

1

2

3

4

5

6

7

8

9

1

2

3

4

5

6

7

8

9

3207 FO2

Figure 2. Bit Assignments

SDA

t SU, DAT

t SU, STA

t BUF

SCL

t

HD, STA

t LOW

t HIGH

t HD, DAT

t HD, STA

t SP

t SU, STO

3207 F03

START

CONDITION

t r

t f

REPEATED START

CONDITION

STOP

CONDITION

START

CONDITION

Figure 3. Timing Parameters

3207fc

11

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

LTC3208EUH#TRPBF

IC LED DRIVR QVGA DISPLAY 32-QFN

LTC3209EUF-2#TRPBF

IC LED DRIVR QVGA DISPLAY 20-QFN

LTC3210EPD-1#TRPBF

IC LED DRVR WHITE BCKLT 16-UTQFN

LTC3210EUD#TRPBF

IC LED DRIVR WHITE BCKLGT 16-QFN

LTC3212EDDB#TRPBF

IC LED DRIVER RGB 12-DFN

LTC3214EDD#TRPBF

IC LED DRIVR WHITE BCKLGT 10-DFN

LTC3215EDD#PBF

IC LED DRIVR WHITE BCKLGT 10-DFN

LTC3217EUD#TRPBF

IC LED DRVR FLASH TORCH 16QFN

相关代理商/技术参数

LTC3207EUF-1-PBF

制造商:LINER 制造商全称:Linear Technology 功能描述:600mA Universal Multi-Output LED/CAM Driver

LTC3207EUF-1-TRPBF

制造商:LINER 制造商全称:Linear Technology 功能描述:600mA Universal Multi-Output LED/CAM Driver

LTC3207EUF-PBF

制造商:LINER 制造商全称:Linear Technology 功能描述:600mA Universal Multi-Output LED/CAM Driver

LTC3207EUF-TRPBF

制造商:LINER 制造商全称:Linear Technology 功能描述:600mA Universal Multi-Output LED/CAM Driver

LTC3208

制造商:LINER 制造商全称:Linear Technology 功能描述:High Current Software Confi gurable Multidisplay LED Controller

LTC3208EUH

制造商:LINER 制造商全称:Linear Technology 功能描述:High Current Software Confi gurable Multidisplay LED Controller

LTC3208EUH#PBF

功能描述:IC LED DRIVR QVGA DISPLAY 32-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - LED 驱动器 系列:- 标准包装:6,000 系列:- 恒定电流:- 恒定电压:- 拓扑:开路漏极,PWM 输出数:4 内部驱动器:是 类型 - 主要:LED 闪烁器 类型 - 次要:- 频率:400kHz 电源电压:2.3 V ~ 5.5 V 输出电压:- 安装类型:表面贴装 封装/外壳:8-VFDFN 裸露焊盘 供应商设备封装:8-HVSON 包装:带卷 (TR) 工作温度:-40°C ~ 85°C 其它名称:935286881118PCA9553TK/02-TPCA9553TK/02-T-ND

LTC3208EUH#TRPBF

功能描述:IC LED DRIVR QVGA DISPLAY 32-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - LED 驱动器 系列:- 标准包装:6,000 系列:- 恒定电流:- 恒定电压:- 拓扑:开路漏极,PWM 输出数:4 内部驱动器:是 类型 - 主要:LED 闪烁器 类型 - 次要:- 频率:400kHz 电源电压:2.3 V ~ 5.5 V 输出电压:- 安装类型:表面贴装 封装/外壳:8-VFDFN 裸露焊盘 供应商设备封装:8-HVSON 包装:带卷 (TR) 工作温度:-40°C ~ 85°C 其它名称:935286881118PCA9553TK/02-TPCA9553TK/02-T-ND